# Projects for Veek-MT2 board in Intel Quartus Lite V20.1 or V23.1

Version 1.3 from 10-Sep-24, published under GNU Free Documentation License

© Richard Šusta 2023, Department of Control Eng.,

Faculty of Electrical Engineering

Czech Technical University in Prague

### **Table of Contents**

| 1.       | Α   | About names and filenames                       | 1  |

|----------|-----|-------------------------------------------------|----|

| 2.       |     | nitial Configuration                            |    |

| 2.<br>3. |     | Project Wizard of the First Project             |    |

|          | 3.1 |                                                 |    |

|          | 3.2 |                                                 |    |

|          | 3.3 |                                                 |    |

| 4.       | C   | Checking your Project                           | 13 |

| 5.       | T   | The Express Copy of a Created Project           | 15 |

| 6.       | V   | Working with Projects                           | 17 |

|          | 6.1 | Reorganizing files in Project Navigator         | 17 |

|          | 6.2 | How to specify Top-Level Entity                 | 18 |

|          | 6.3 | Moving and zipping our project                  | 18 |

|          | 6.4 | Changing Revision = Compilation Result Filename | 21 |

#### 1. About names and filenames

Beware, Quartus is a Unix program that runs in Cygwin, an extensive collection of GNU and Open Source tools that provide functionality similar to a Linux distribution on Windows. Thus, all folders and files should satisfy strict Unix name rules.

The filenames can contain upper and lower case ASCII letters, numbers, dots "." and underscore "\_". Do not use spaces and special characters. For completeness, some Linux versions allow them, but we have bad experiences with their usage in Cygwin. You can try to see if they work for you, but if not, complain to yourself.

We recommend using only ASCII letters and numbers in Quartus entity names. They usually correspond with filenames because one entity is stored in the file of the same filename. Its identifier must start with a letter, the last character cannot be an underscore, and two connected underscores are not allowed. However, the entity names with underscores can sometimes collapse the internal Quartus simulator. We do not find out why. It just sometimes happens. It is better to avoid underscores.

VHDL is not case-sensitive, but we should keep capitalization. If we define the symbol Data, the wrong style refers to it as "data" or "DATA".

VHDL does not understand diacritics and non-ASCII characters, not even in comments.

# 2. Initial Configuration

Before creating your first project, you should perform permanent global configurations that will be reflected in all the following projects.

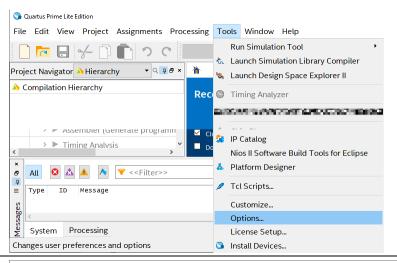

Select **Option** from Quartus menu Tools:

We begin by the General tab, specifying the default directory for storing our projects. Its choice is ours.

We recommend also checking:

"Show full file path in window titles" to improve orientation.

## **EDA Tool Options**

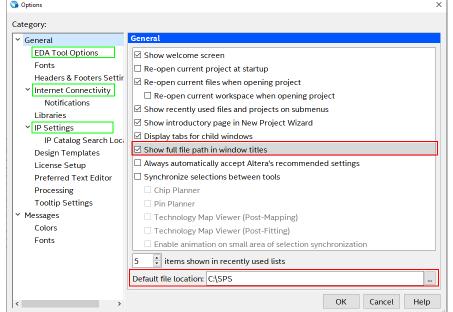

#### **Ouartus Version 20.1**

Then, we proceed to EDA Tool Options and set the path to ModelSim-Altera to ensure it will always be located.

We find it in subfolder modelsim\_ase\win32aloem of the install directory. The default is:

C:\intelFPGA lite\20.1\

2

### **Quartus Version 23.1**

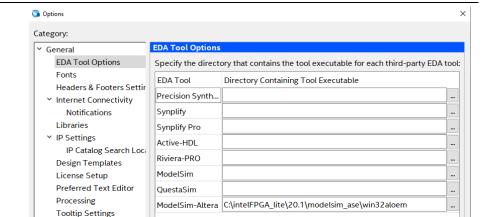

We then go to EDA Tool Options and set the path to Intel-Questa to ensure it is always located.

It can be found in the subfolder questa\_fse/win64 installation directory. The default value is: c:/intelfpga\_lite/23.1std/

Note: IP is Intelligent Property here.

Category: **EDA Tool Options** General Specify the directory that contains the tool executable for each Directory Containing Tool Executable EDA Tool Headers & Footers Setting Internet Connectivity Precision S... Libraries Synplify IP Settings IP Catalog Search Local Synplify Pro Design Templates Active-HDL License Setup Riviera-PRO Preferred Text Editor Processing ModelSim **Tooltip Settings** QuestaSim Messages Questa Intel... c:/intelfpga\_lite/23.1std/questa\_fse/win64 Fonts

Note: The acronym EDA here refers to Electronic Design Automation tools that chip designers use to analyze entire semiconductor chips. The Quartus installation contains only one free tool, ModelSim Altera, i.e., ModelSim with embedded Quartus FPGA libraries, V23.1 Questa.

We can also set our default browser. Category: General Quartus uses it to display its helps. **EDA Tool Options** Web browser Fonts  $\ensuremath{\square}$  Use custom web browser instead of system default Headers & Footers Settin ... Path: "C:\Program Files\Google\Chrome\Application\chrome.exe" Internet Connectivity In IP Setting category, select VHDL. IP Settings IP Catalog Search Loca IP generation HDL preference: VHDL ▼

If you wish, you can adjust the primary and message fonts and, eventually, other options.

Design Templates

Options

Finally, close the Option dialog by [OK] button to store changes; otherwise, the changes will be canceled.

Then, close Quartus Prime and **rerun it** so Quartus starts with new options!!!!

### 3. Project Wizard of the First Project

Creating our first project is complicated by many settings, but it is one one-time task; the following projects are made in a minute; see Chapter 5 on page 15.

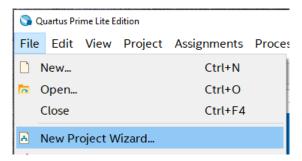

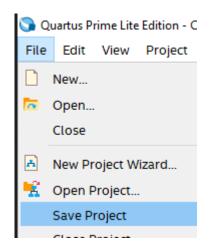

From the main menu Quartus, we choose File-> New Project Wizard.

The Wizard's dialog consists of several pages; you can scroll from one page to another, forward by [Next], and backward by [Back].

► **Introduction** — continue by [Next >]

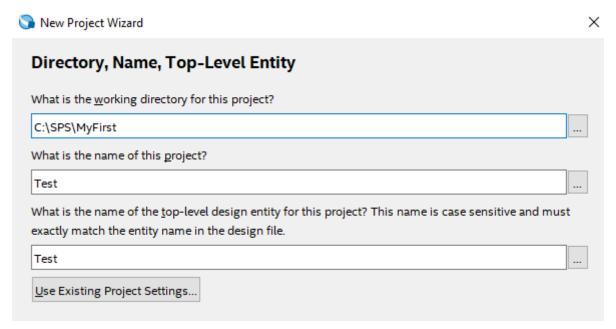

# **▶** Directory, Name, Top-Level Entity

Enter any folder name inside an existing directory, e.g., "MyFirst" — the folder should not exist yet; it will be created. We also choose names for our project and entity, e.g., "Test". Do not use anything that could accidentally be an HDL language keyword, such as "else", "input", "output", and so on.

After entering all items, click the [Next >] button and confirm the creation of a new directory. If you look at this question, it is a good sign that Quartus projects do not share its directories.

*Note 1:* Quartus does not allow the storage of two projects in one folder! Each project has its directory.

**Note 2:** Unlike older Quartus versions, the button [Use Existing Project Settings] does not allow copying many settings in Quartus 20.1. We show the better way on page 13.

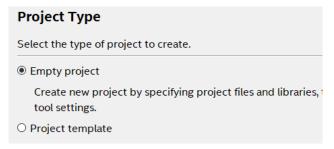

▶ **Project Types** —We select Empty and press [Next >] because project templates do not exist for our educational board Veek-MT2.

- ► Add Files skip by [Next >]

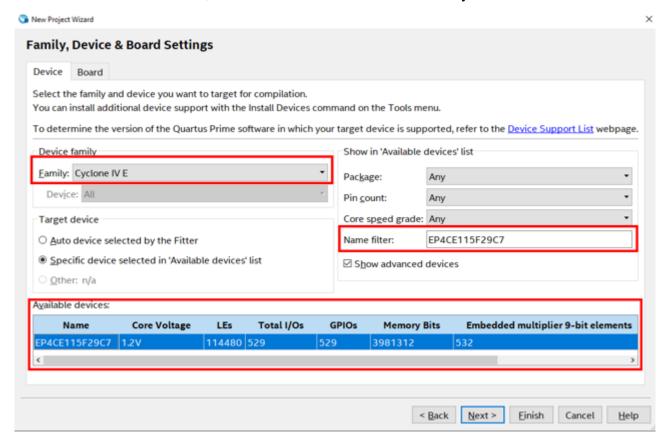

- ► Family Device & Board Settings —enter the following for development board Veek-MT2:

- First, we must set the family: Cyclone IV E

- Then, we write/copy in the name filter: EP4CE115F29C7

In the list of available devices, we select FPGA EP4CE115F29C7 by mouse double click.

Click [Next>]

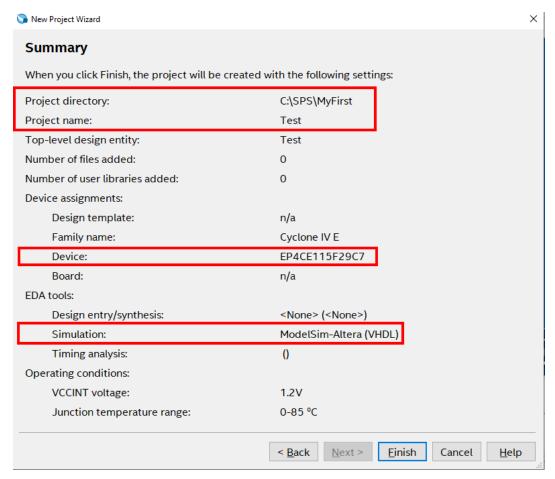

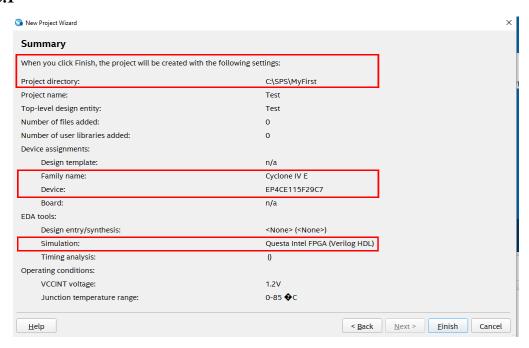

# ► **Summary** – check if everything is OK.

### **Version Qurtus 20.1**

### Version Q23.1

If it is OK, click [Finish].

# 3.1 Additional Project Setting for Board Veek-MT2

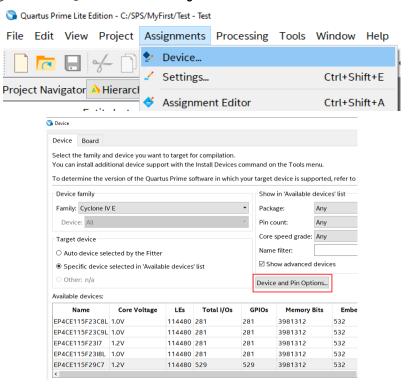

Open the Device dialog from the Quartus menu Assignments->Device:

We saw this dialog in Project Wizard, but now, the new button [Device and Pin Options] appears here. Click on it and select in the Dual-Purpose Pins tab that nCEO pin of FPGA will be used as regular I/O.

By [OK] buttons, we first close the sub dialog "Device and Pin Options" and then the "Device" dialog.

Note: Pin nCEO (Chip Enable Output) allows in JTAG communication the selection of an FPGA device, to which we download configuration.

VEEK-MT2 board contains only one FPGA chip, which is always selected, so it utilizes free nCEO as programming pin (for LCD color bit); therefore, we must inform Quartus about nCEO modification.

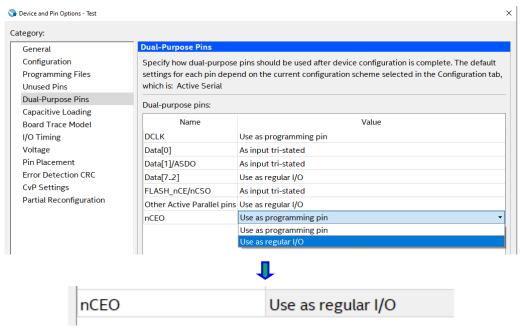

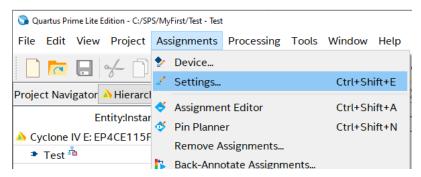

# 3.2 ► Setting up EDA tools

Invoke the Settings dialog from the Quartus menu:

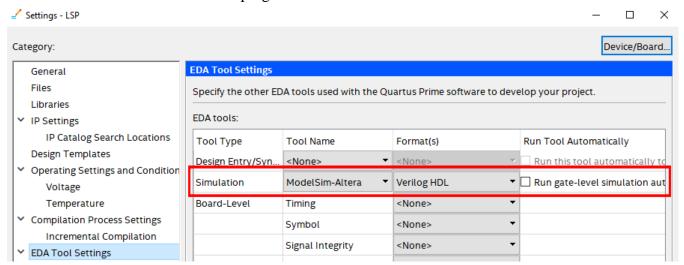

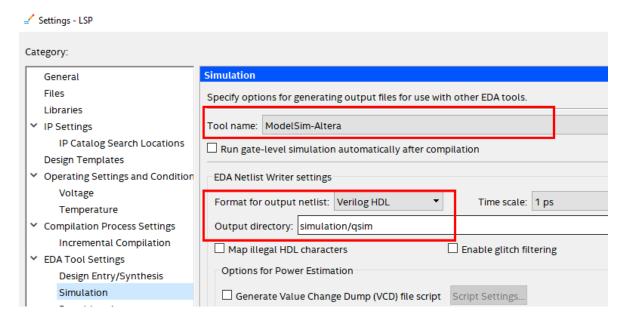

In its Category tree, select EDA Tool Settings. Set up the simulation tool to ModelSim Altera in VHDL. Do not change anything else here

**Version 20.1-** Set Model-Sim-Altera in VHDL and leave the other items in their default state! The free version does not contain other EDA programs.

Change also the simulation output directory to simulation/qsim – the internal simulator of Quartus.

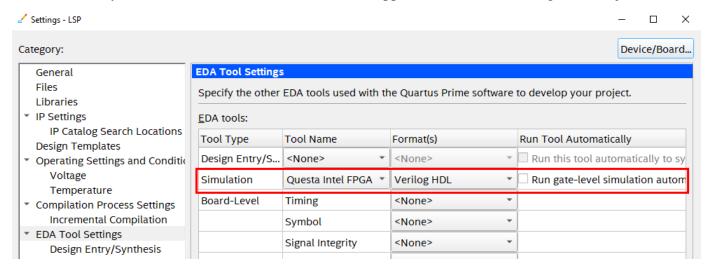

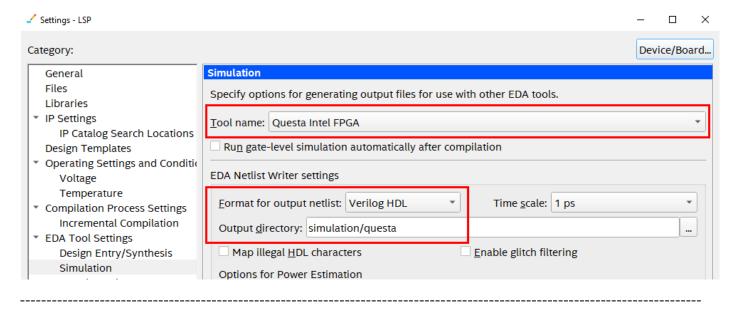

### Version 23.1

Just make sure you have the Questa Simulator. It should appear as the default setting, if not adjust.

Check the simulation output directory; it should be to simulation/questa – the external free simulator.

Finally, we close the Setting dialog by the [OK] button to accept data.

### 3.2.a. Compiler

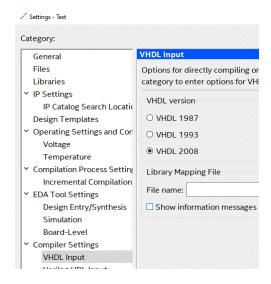

In the Compiler Category -> VHDL Input category, check VHDL 2008.

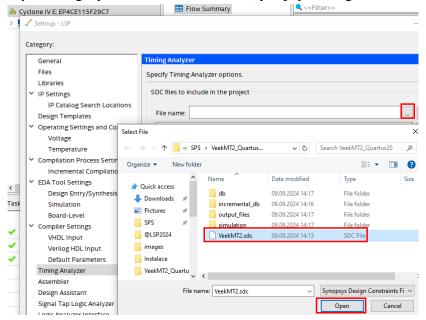

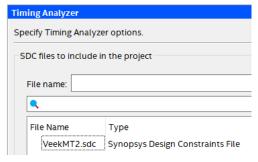

# 3.3 TimeQuest Setting

From the default project, copy the VeekMT2.sdc file to the main project folder and then on the Settings dialog, in the Timing Analyzer category, look for the \*.sdc file (Synopsys Design Constraints).

Add it into the Timing Analyzer constraints file list.

Note: The \*.sdc files inform Quartus that the VEEK-MT2 teaching board contains a 50 MHz clock generator. The clock frequency is a critical specification. Without this information, our circuit will be built for a default frequency of 1 GHz. The internal circuitry of FPGAs depends on the frequency, as we explain in our lectures, so the result will be non-functional.

Finally, close the Settings dialog box with **[OK] and** accept the data.

# 3.4 Pin Assignments

FPGA chip used in VEEK-MT2 has 780 solder balls arranged in a grid or array at the bottom of the package body for external electrical connections; see the left picture [source Intel]. Each solder ball is internally one pin.

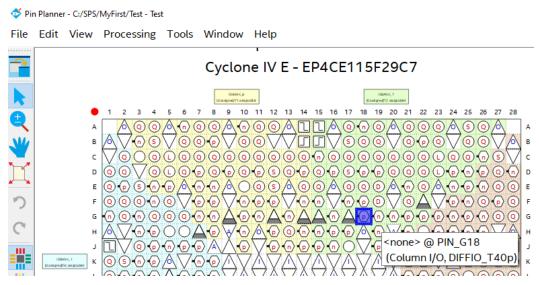

Users can direct inputs or outputs of their circuit designs up to 528 pins. This possibility can simplify printed board designs. The pins are indexed with a letter and a number. We can see them in Pin Planner.

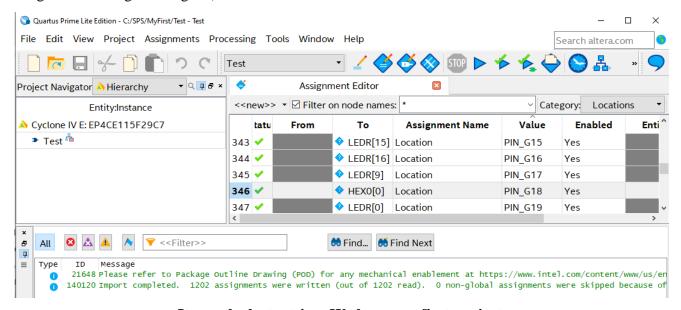

We work with a ready-made board; therefore, we must follow their placement by loading the manufacturer's pin assignments. Their absence is a frequent error in beginner's designs. Always check if the Assignment Editor shows pins and not an empty list as below:

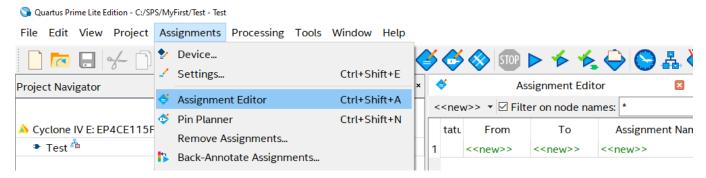

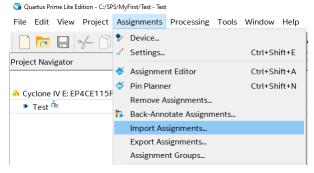

The original pin indexes are complex to remember, so we import their association with their symbolic names defined by the Pin Assignment spreadsheet table. In the main Quartus menu, select:

### **Assignments->Import Assignments.**

From the default Quartus project, copy VeekMT2\_PinAssignments.csv to your Quartus project root folder.

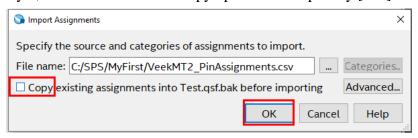

In the Import Assignment dialog, browse for the copied file VeekMT2\_PinAssignments.csv.

We confirm the choice by [Open] and then [OK] buttons.

We have no assignment yet, so we unchecked the copy option. We import by [OK].

If we look at **Assignments-> Assignment Editor**, the list now contains associations. We can find out that PIN\_G18 from the previous pin planner figure was named HEX0[0], i.e., it is the upper led segment in the least significant 7-segment digit :-)

It was the last setting. We have our first project.

~ 0 ~

Never edit the pin assignment list; keep compatibility by using predefined names!

# 4. Checking your Project

Quartus projects require many settings that are easy to make mistakes in.

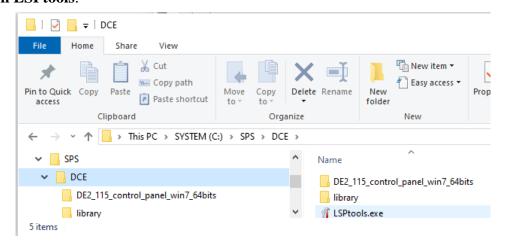

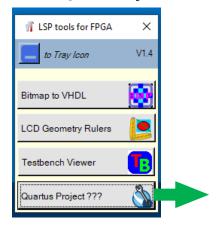

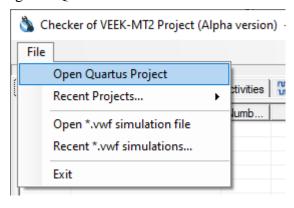

Richard Šusta, the teacher of the LSP course in Dept. of Control Eng., CTU-FEE in Prague, created the LSPTools program, which includes the project verifier in Quartus. It is open source and will soon be hosted on GitHub. **Run LSPtools**:

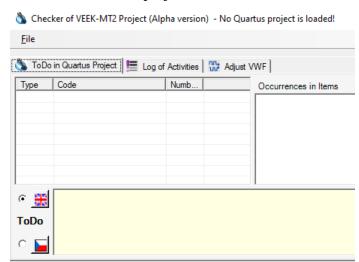

Select [Quartus Project ????] in the main windows to start the project checker.

In Quartus, save the project so the checker can read its actual settings.

And open the project from the checker without closing it in Quartus.

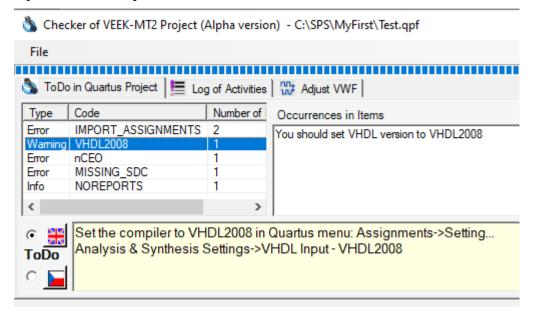

We will see it all in the reports if we have forgotten something. The picture below shows the check result of the previously correct project, now intentionally modified to demonstrate the checker. Clicking on the reports, we see help on how to remove them

We perform corrections, save the project, and recheck it until all errors and warnings disappear.

Note: Type NOREPORTS belongs to an information message that the project does not contain compilation results, so their analysis could be performed.

# 5. The Express Copy of a Created Project

If I have already created at least one complete project from scratch, we can copy it to obtain another project in a minute.

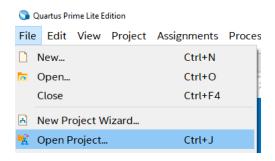

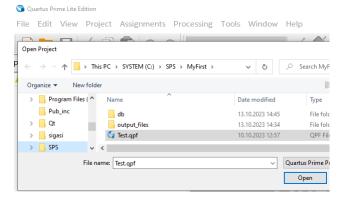

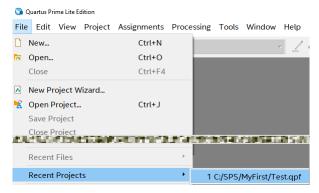

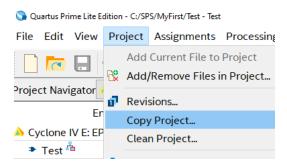

From the Quartus menu, we open any of our projects, e.g., we use MyFirst:

Eventually, we can access it from the "Recent Project" offer:

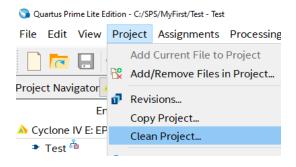

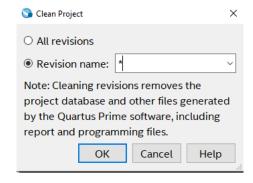

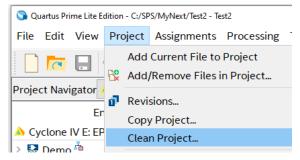

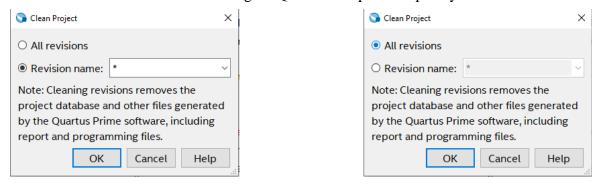

First, we select "Project-> Clean project" to remove all temporary files, and by [OK], we confirm either the default option or All revisions.

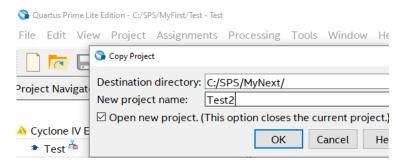

Then, we open the "Project->Copy Project" dialog. We enter our project name, e.g., Test2, and specify a directory where we want to store its files.

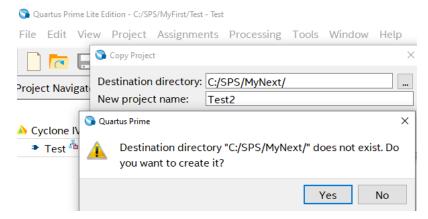

After confirming our choice by [OK], the message below signals that we are creating our project in the new directory, which will be its own, as required.

We have already created our new project with all the necessary settings. It also contains all the Test project files.

The following chapter explains how

- to change Top-Level Entity;

- to adjust our project by adding new files or removing unused ones;

- to move our project to another directory or computer;

- to change the compilation result file name.

### 6. Working with Projects

The following steps are more adjustments than requirements.

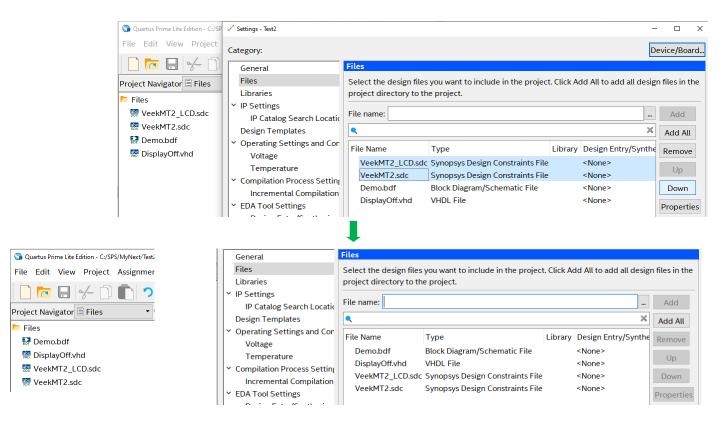

# 6.1 Reorganizing files in Project Navigator

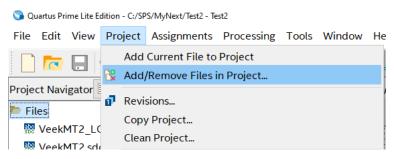

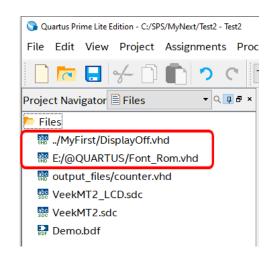

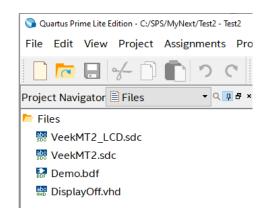

From the file dialog, we can reorganize files in our project.

It is possible to add new files or remove ones no longer needed. The changes are performed only in the list. Files are not deleted from the hard drive; any file explorer can do it.

We always keep all our design files in the directory of the project. We easily recognize wrongly placed items by their extra path.

In the left figure, wrongly located files are marked by red box.

The first one

../MyFirst/DisplayOff.vhd

is in the parent's subfolder:

C:/SPS/MyFirst/DisplayOff.vhd

i.e., outside our project.

The second file

E:/@QUARTUS/Font Rom.vhd

is stored even on a different drive.

The third file

#### counter.vhd

is in a subfolder output\_files of our project. It is acceptable but not recommended for small projects.

The preferable file locations are in the project directory, i.e., without paths.

Eventually, we can rearrange the Project Navigator list with buttons [Up] or [Down]. Then, we confirm the changes by clicking [OK] button.

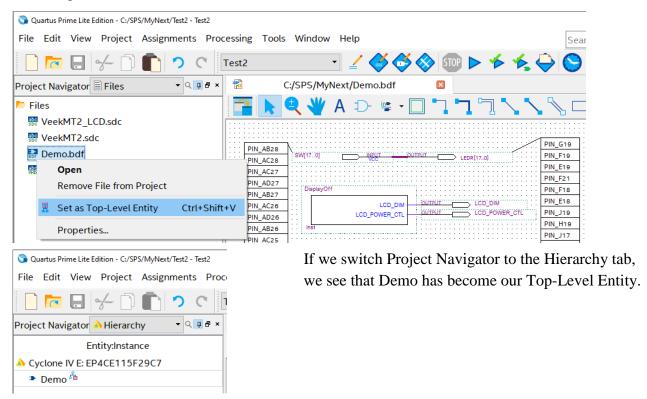

# 6.2 How to specify Top-Level Entity

Our Top-Level Entity selects the design file from which the compilation begins. After we write down some synthesis files, we can dedicate anyone as the Top-Level Entity from the Project Navigator Files.

For instance, we add DisplayOff.vhd, extracted from the zip mentioned in Chapter 3.3 on page 10, and create a simple Demo.bdf that copies slider switches to red LEDs. Then, we mark it as a Top-Level entity from its context menu (a right mouse click on file).

# 6.3 Moving and zipping our project

Quartus is very versatile. We can open a project created in version 20.1 in some of its previous versions, e.g., in Quartus 13.1, and any lower version project in upper Quartus.

If we have all files in the project directory, as was explained in the previous chapter, Quartus keeps their path relative. So we can rename the project's root directory or move it to another location.

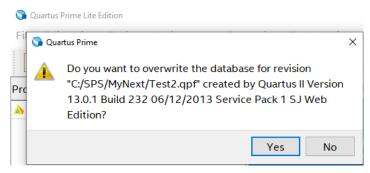

When we move our project to a different computer, directory, or Quartus version, we can see a message similar to the picture below:

We should always confirm [YES] if we have a small project.

Note: Compiling huge industrial designs can sometimes last for several hours. Therefore, the Quartus asks if we allow deleting previous results. It is better to let the Quartus begin with clean intermediate databases in small projects.

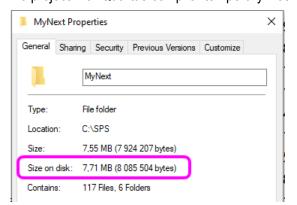

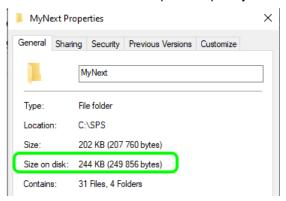

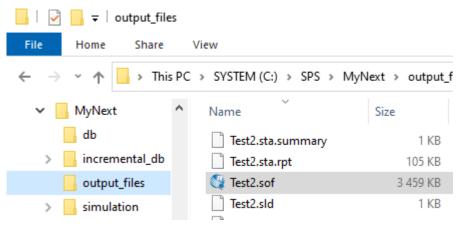

However, our tiny project can surprisingly contain many temporary files created during compilation and placement into an FPGA chip; see the figure below.

The project with Quartus compiler temporary files

without the Quartus compiler temporary file

Even if our design had a few files, the FPGA is big. The compiler needs to configure everything in its whole chip, i.e., in our case, it mostly deactivates non-used parts.

We can reduce the project size by removing temporary files before zipping or copying the project to a USB stick by the Project -> Clean Project, equivalent to the "make clean" command in classic programming.

Any of the selections below leads to removing all Quartus compiler temporary files.

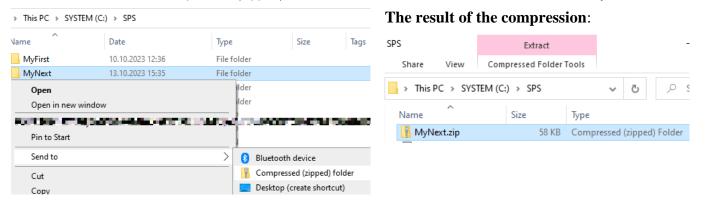

Then, we close the Quartus to release its locked files and run the File Explorer.

We select the Send to->Compressed (zipped) folder from the context menu of the root directory folder.

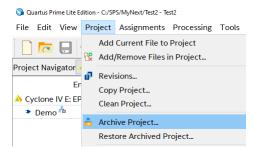

Note: We prefer zip to the Quartus menu command the "Archive Project":

Its result has an internal format \*.qar that can be depacked only by Quartus. The zip file is more versatile.

# 6.4 Changing Revision = Compilation Result Filename

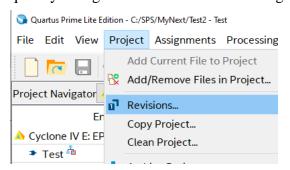

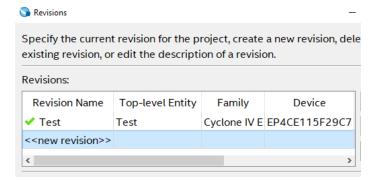

The compilation generates the result, which filename is derived from the revision name. For example, the result can be Test.sof (sof=SRAM Object File). The Revision is also copied with the project. We can quickly change it from the Revision dialog:

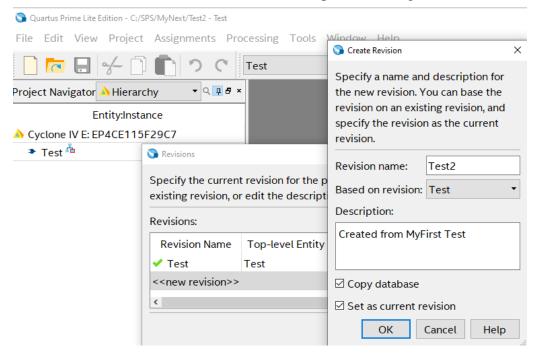

By mouse double click into <<new revision>> table row, we open sub dialog:

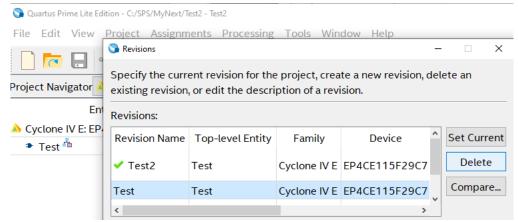

We enter, for example, Test2 as the name of our new project and possibly some description if we wish. After confirming by [OK], we again open the menu: Project ->Revisions.

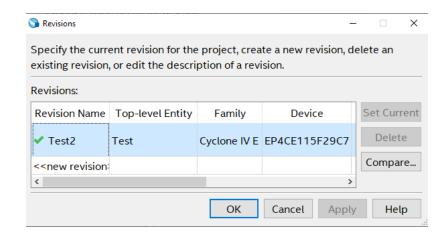

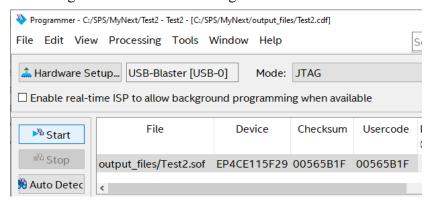

After deleting the old revision Test, we obtained the project, which compilation leads to Test2.sof.

The result Test2.sof can be downloaded into the FPGA chip by the Quartus programmer.

The Quartus menu: Tools->Programmer shows the dialog below.

We explain its setting in practical exercises of our LSP course. Its brief explanation is on page 40 of the document:

### https://dcenet.fel.cvut.cz/edu/fpga/de2-115/My\_First\_Fpga.pdf

Note: VEEK-MT2 is a combo of LCD and DE2-115 board; thus, DE2-115 manuals are valid, but DE2-115 Pin Assignments define only a part of VEEK-MT2 pin assignments.

The programmer's more advanced functions, which we do not use in the LSP course, are described in the Intel document:

https://www.intel.com/content/www/us/en/docs/programmable/683039/20-4/introduction.html

\*\*\* The End \*\*\*